19/952

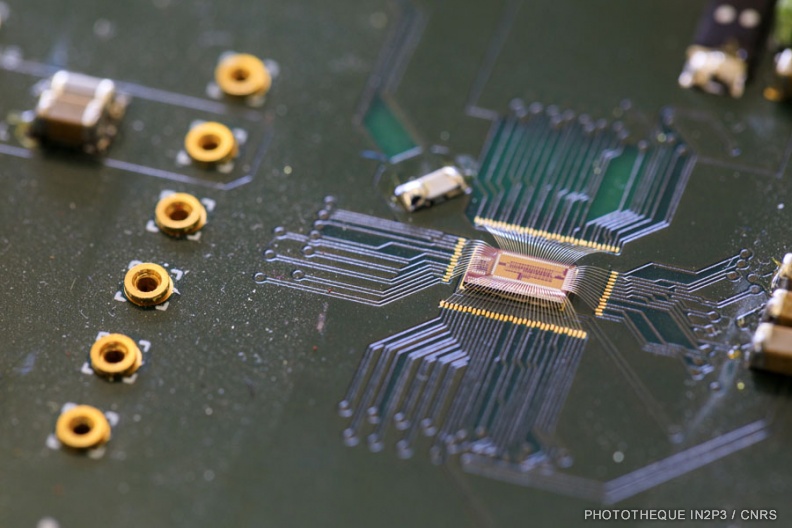

Puce silicium Shunt LDO (©CPPM) en technologie TJ180nmn micro-câblée sur circuit imprimé pour des tests de caractérisation de la technologie Depleted CMOS en vue de futurs projets tels que Belle II

- Auteur

- Camille Moirenc

- Créée le

- Vendredi 27 Novembre 2020

- Ajoutée le

- Lundi 12 Décembre 2022

- Dimensions

- 900*600

- Fichier

- 139_MOIRENC_CPPM_NOV2020.jpg

- Poids

- 121 Ko

- Mots-clés

- capteur CMOS, CPPM, Puce

- Albums

- Visites

- 334

- Téléchargements

- 0