Accueil \ Laboratoires de recherche \ CPPM - Centre de physique des particules de Marseille \ Instrumentation et Technologies \ Activités Electronique 26

Carte PCle400

Carte PCle400 Carte PCle400

Carte PCle400 R&D en détecteurs et instrumentation

R&D en détecteurs et instrumentation Carte PCIe40 d'acquisition de données de l'expérience LHCb

Carte PCIe40 d'acquisition de données de l'expérience LHCb Carte PCIe40 d'acquisition de données de l'expérience LHCb

Carte PCIe40 d'acquisition de données de l'expérience LHCb Prise de vue artistique d'une carte électronique

Prise de vue artistique d'une carte électronique Carte PCIe40 d'acquisition de données de l'expérience LHCb

Carte PCIe40 d'acquisition de données de l'expérience LHCb LHCb serveur PCIe40

LHCb serveur PCIe40 Carte PCIe40 d'acquisition de données de l'expérience LHCb

Carte PCIe40 d'acquisition de données de l'expérience LHCb Carte PCIe40 d'acquisition de données de l'expérience LHCb

Carte PCIe40 d'acquisition de données de l'expérience LHCb Carte PCIe40 (©CPPM)

Carte PCIe40 (©CPPM) Banc de test de la carte PCIe40 (©CPPM) et caractérisation des liens sériels optiques 5 Gbps pour l'expérience LHCb

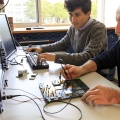

Banc de test de la carte PCIe40 (©CPPM) et caractérisation des liens sériels optiques 5 Gbps pour l'expérience LHCb La carte INTERMEZZO (©CPPM), ici montée sur une carte ©ReflexCES

La carte INTERMEZZO (©CPPM), ici montée sur une carte ©ReflexCES Emetteur-récepteur optique 25 Gbps monté sur la carte INTERMEZZO (©CPPM) pour l'expérience ATLAS

Emetteur-récepteur optique 25 Gbps monté sur la carte INTERMEZZO (©CPPM) pour l'expérience ATLAS Banc de tests et caractérisation de la transmission de données haute vitesse (25 Gbps) de la carte INTERMEZZO (©CPPM) pour l'expérience ATLAS

Banc de tests et caractérisation de la transmission de données haute vitesse (25 Gbps) de la carte INTERMEZZO (©CPPM) pour l'expérience ATLAS Carte INTERMEZZO d’extension du nombre de liens optiques haute vitesse (25 Gbps) montée sur la carte de développement Stratix-10 ©ReflexCES pour l'expérience ATLAS

Carte INTERMEZZO d’extension du nombre de liens optiques haute vitesse (25 Gbps) montée sur la carte de développement Stratix-10 ©ReflexCES pour l'expérience ATLAS Banc de mesure-contrôle-commande de la séquence d’alimentation du FPGA Stratix-10 embarqué sur la carte LASP (Liquid Argon Signal Processor, ©CPPM) pour l'expérience ATLAS

Banc de mesure-contrôle-commande de la séquence d’alimentation du FPGA Stratix-10 embarqué sur la carte LASP (Liquid Argon Signal Processor, ©CPPM) pour l'expérience ATLAS Vue d’artiste de la carte DAQTEMP (©CPPM) destinée à l’acquisition des signaux SiPM (Silicon PhotoMultiplier) pour le projet TEMPORAL

Vue d’artiste de la carte DAQTEMP (©CPPM) destinée à l’acquisition des signaux SiPM (Silicon PhotoMultiplier) pour le projet TEMPORAL Mesure de la chaine analogique de la carte DAQTEMP (©CPPM) pour le projet TEMPORAL

Mesure de la chaine analogique de la carte DAQTEMP (©CPPM) pour le projet TEMPORAL Câblage de la carte électronique Sensor Board (©CPPM) équipée de capteurs de température et destinée au test et à la caractérisation de liaisons I2C lors de la conception de la carte LASP (Liquid Argon Signal Processor, ©CPPM) pour l'expérience ATLAS

Câblage de la carte électronique Sensor Board (©CPPM) équipée de capteurs de température et destinée au test et à la caractérisation de liaisons I2C lors de la conception de la carte LASP (Liquid Argon Signal Processor, ©CPPM) pour l'expérience ATLAS Micro-soudure sur la carte électronique Sensor Board (©CPPM)

Micro-soudure sur la carte électronique Sensor Board (©CPPM) Micro-soudure sur la carte électronique Sensor Board (©CPPM)

Micro-soudure sur la carte électronique Sensor Board (©CPPM) Inspection à la loupe numérique des soudures de la carte Intermezzo (©CPPM) de retour de câblage par un prestataire pour l'expérience ATLAS

Inspection à la loupe numérique des soudures de la carte Intermezzo (©CPPM) de retour de câblage par un prestataire pour l'expérience ATLAS Banc de tests et caractérisation en irradiation des puces prototypes TSMC65nm (©CPPM) dans le cadre du projet RD53

Banc de tests et caractérisation en irradiation des puces prototypes TSMC65nm (©CPPM) dans le cadre du projet RD53 Puce silicium Shunt LDO (©CPPM)

Puce silicium Shunt LDO (©CPPM) Puce prototype Monitoring ADC (©CPPM)

Puce prototype Monitoring ADC (©CPPM)